Verilog / Implementing 4to1 mix using 2to1 mux only

Optimizing 8 to 1 Multiplexers for Shorter Delay in VerilogПодробнее

16:1 mux using 4:1 mux | Implement 16×1 multiplexer using 4×1 multiplexerПодробнее

4X1 Mux Using Transmission GateПодробнее

Design All Types of Gates using 2:1 MUX only || Digital important question || ECE || VLSI || #4Подробнее

IMPLEMENTATION of 8X1 MUX using 4X1 and 2X1 || VERILOG CODE ||TEST BENCH || Digital ElectronicsПодробнее

4 to 1 Mux using 2 to 1 Mux || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

VLSI Interview Questions | Implementing 16:1 MUX using 5:1 MUX and 5:1 MUX using 2:1 MUXПодробнее

5 to 1 Mux Using 2 to 1 Mux || VLSI Design || Learn Thought || S Vijay MuruganПодробнее

VLSI Interview Mastery: Implementing 16x1 Mux with 8:1 Mux and 2:1 Mux | 10x1 Mux with 4x1 MuxПодробнее

Implementation of 2×1 MUX using NAND & NOR GatesПодробнее

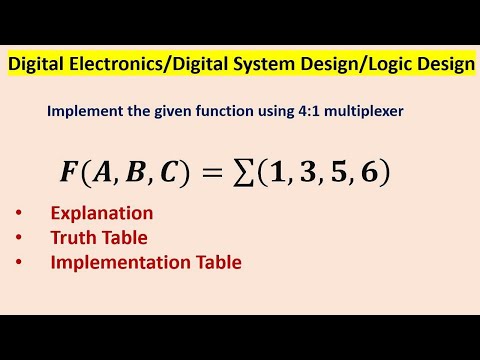

Implement the given function using 4:1 multiplexer. 𝑭(𝑨,𝑩,𝑪)=∑(𝟏,𝟑,𝟓,𝟔)Подробнее

How to implement 2:1 Mux using tri-state buffer in verilogПодробнее

implement 8X1 MUX using 4X1 MUXПодробнее

Implementation of NAND Gate using 2:1 Mux in verilogПодробнее

Implementing Not Gate using 2:1 Mux in VerilogПодробнее

Function syntax in Verilog(4:1 mux implementation using 2:1 mux)Подробнее

Half Adder Implementation using 2 to 1 Multiplexer || Half adder using 2x1 Multiplexer | STLD | DLDПодробнее

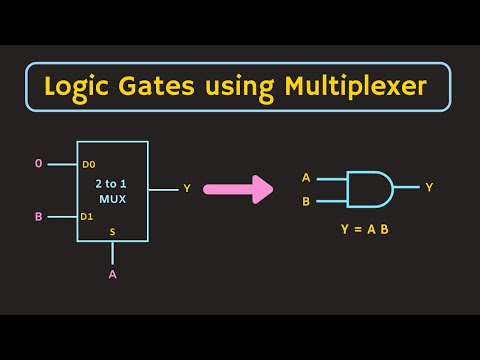

Logic Gates using Multiplexer | How to implement a logic gate using the multiplexer ?Подробнее

16:1 mux Using 4:1 mux || TeluguПодробнее