Implementation of 2×1 MUX using NAND & NOR Gates

Multiplexer as Universal Logic | All Logic Gates Using 2-to-1 MUX ExplainedПодробнее

How to Implement AND, OR, NOT, NAND, NOR, XOR, XNOR gates using 2:1 MultiplexerПодробнее

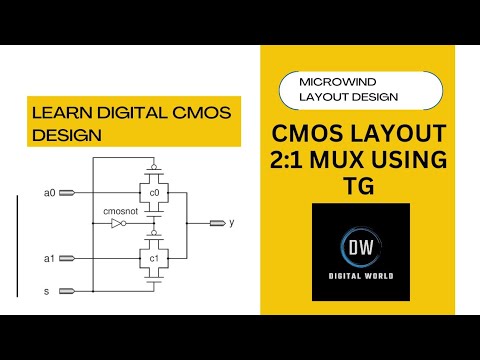

2:1 Multiplexer and 4:1 Multiplexer using CMOS transmission GatesПодробнее

Design a 4-to-1 Line multiplexer using only NAND gates | SolutionПодробнее

IMPLEMENTATION OF NAND AND NOR GATE USING 2X1 MULTIPLEXER || DIGITAL ELECTRONICSПодробнее

Logic design using multiplexer | How to implement all the logic gates by using 2:1 multiplexer?Подробнее

DIGITAL ELECTRONICS LAB EXPERIMENT 9 | 4x1 MULTIPLEXER | KTU IN MALAYALAMПодробнее

Design of 2×1 Multiplexer using transmission gate logic in Cadence Virtuoso #cadence #virtuoso #vlsiПодробнее

LAB EXPERIMENT ON 4:1 MULTIPLEXER USING GATESПодробнее

NAND gate using multiplexer | implement NAND gate using 2x1 MUXПодробнее

Design 2 to 1 Mux Using CMOS Switch || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

8 to 1 Mux Using 2 to 1 Mux || Test Bench Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

8 to 1 Mux Using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

4 to 1 Mux using 2 to 1 Mux || Test Bench Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

4 to 1 Mux using 2 to 1 Mux || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

NAND Gate using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

CMOS 2:1 MULTIPLEXER USING TRANSMISSION GATEПодробнее

Verilog HDL Code for Implementation of AND,OR and NOT Gate Using 2 to 1 MUX || Learn ThoughtПодробнее

CMOS LAYOUT OF INVERTERПодробнее

Implementation of EX OR and EX NOR Gate Using 2 to 1 Multiplexer || Learn Thought || S Vijay MuruganПодробнее