LECTURE 8 / Full 4 bit adder / Verilog

8 to 1 Mux Using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

How to design and Write Verilog code for Carry LOOK Ahead Adder? || Learn Thought || S Vijay MuruganПодробнее

Design of 4 bit Comparator || Verilog HDL Program || Learn Thought || S VIJAY MURUGANПодробнее

Design of 1:8 Demultiplexer using Verilog Data flow Model | Learn Thought | S VIJAY MURUGANПодробнее

Serial Adder (Ripple Carry Adder): Design and Circuit Explained | COAПодробнее

Design of 4 Bit Counter | Verilog HDL Program | Learn Thought | S VIJAY MURUGANПодробнее

Design of 8 to 3 Encoder Using Verilog HDL | VLSI Design | S VIjay MuruganПодробнее

Design a Verilog Code for 2 to 4 Decoder | VLSI Design | S VIJAY MURUGANПодробнее

4-Bit Ripple Carry Adder Verilog HDL Program | Gate Level Modeling | VLSI Design | S VIJAY MURUGANПодробнее

4 to 1 MUX Verilog Code using Gate Level Modelling | VLSI Design | S VIJAY MURUGANПодробнее

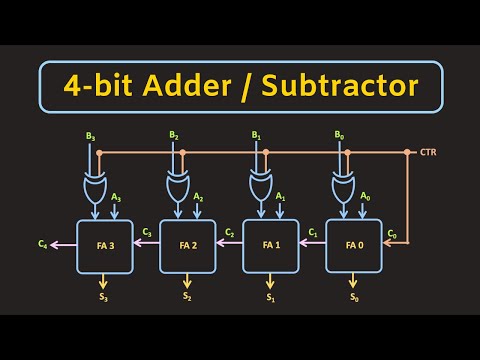

4-bit Adder and Subtractor Circuit ExplainedПодробнее

Ripple Carry Adder Explained (with Solved Example) | Working and Limitation of Ripple Carry AdderПодробнее

8 bit Adder using 2 bit adder Design using Verilog | Hardware modeling using verilogПодробнее

2021 IITR Digital Logic Design: Lecture 8 (Full adder, 4 bit adder, 8 bit adder, XOR Gate with NAND)Подробнее

Verilog HDL: 4-bit Adder using Data Flow ModellingПодробнее

Module 3 - Gate level description of ripple carry adder- lecture 16Подробнее

Verilog HDL (18EC56) | Module 3 | Unit 6 | Dataflow Modelling | Example 3 - 4-bit CLA Adder | VTUПодробнее

Verilog HDL (18EC56) | Module 3 | Unit 5 | Gate level Modelling | Example 2 - 4 bit Adder | VTUПодробнее

Data flow modelling in Verilog and Implementation of BCD Adder in Xilinx ISEПодробнее