Design of 1:8 Demultiplexer using Verilog Data flow Model | Learn Thought | S VIJAY MURUGAN

1 to 4 Demux Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

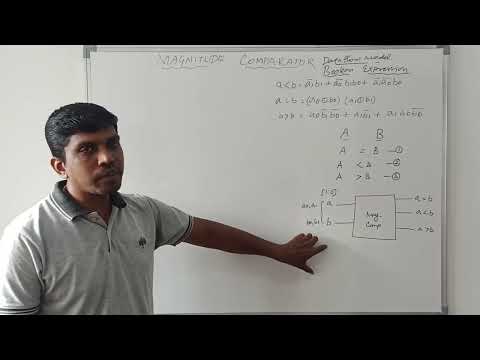

Magnitude Comparator Verilog HDL using Data Flow Model || S Vijay Murugan || Learn ThoughtПодробнее

How to Write 2 to 4 Decoder Verilog HDL Program? // Behavioral Model // S Vijay MuruganПодробнее

Design a 1:4 De-multiplexer using Behavioral Model / VERILOG HDL / S VIJAY MURUGAN / LEARN THOUGHTПодробнее

Design an 8X1 Multiplexer using Behavioral Modeling / Verilog HDL / Learn Thought / S Vijay MuruganПодробнее

Design of 4 bit Comparator || Verilog HDL Program || Learn Thought || S VIJAY MURUGANПодробнее

Design of Half Subtractor Using Data Flow Model -Verilog || Learn Thought | S VIJAY MURUGANПодробнее

Verilog code for Half Subtractor / Learn Thought / S VIJAY MURUGANПодробнее

4 to 1 MUX Verilog Code using Gate Level Modelling | VLSI Design | S VIJAY MURUGANПодробнее