"Full Adder Design Using Gate Level Modeling in Verilog | Xilinx Vivado Tutorial 💻⚙️" Video no.3

"Full Adder Design Using Gate Level Modeling in Verilog | Xilinx Vivado Tutorial 💻⚙️" Video no.3Подробнее

Full adder design and simulation in XILINX Vivado ToolПодробнее

Xilinx ISE: Design and simulate VERILOG HDL CodeПодробнее

Verilog Tutorial: Understanding Structural Modeling and Gate Level Modeling | EP-3Подробнее

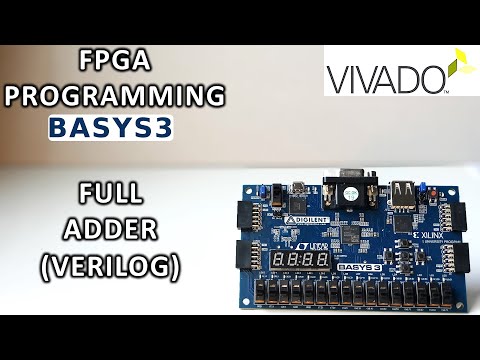

FPGA Programming with Verilog : Full Adder BASYS3Подробнее

ALU Design in Verilog with Testbench | Simulation in Modelsim | Arithmetic Logic UnitПодробнее

Verilog HDL (18EC56) | Module 3 | Unit 5 | Gate level Modelling | Example 2 - 4 bit Adder | VTUПодробнее

4-Bit Full Adder Verilog Code and Testbench in ModelSim | Verilog TutorialПодробнее