Verilog Code (3): Data Flow Modeling

Half Adder in Verilog (Dataflow + Structural Modeling) | Full Code & SimulationПодробнее

|| 3 to 8 Decoder in Gate Level Modeling and Data Flow Modeling in Telugu || DLD through Verilog ||Подробнее

8(B) Verilog : Operators, Data Flow Modeling, and Examples | #30daysofverilogПодробнее

|| 8 to 3 Encoder Using Gate Level Modeling and Data Flow Modeling in Telugu || DLD through Verilog|Подробнее

3-Bit Full Adder Design using Data Flow Modeling in Verilog: Xilinx Vivado | Synthesis & SimulationПодробнее

Logic gates Design in Verilog using Structural ,Data flow and Behavioral Modeling with Test Bench .Подробнее

3 - Verilog : Data Flow Modeling exampleПодробнее

class no #3 Behavioural Model 8:1 Mux verilog code and linear TestbenchПодробнее

MULTIPLEXER- Verilog coding with 3 types of Modeling (Data-flow, Structural, and Behavioural)Подробнее

ANG Gate Verilog HDL Code using Gate | Dataflow | Behavioral ModelingПодробнее

Verilog Code for 8 to 3 encoder in Data Flow, Gate Level and behavioral Model in Telugu with VIVADOПодробнее

Write a Verilog code for 8 to 3 encoder using Gate Level, Data Flow & Behavioral Model | VIVADOПодробнее

How to write a Verilog code in Data Flow & Gate Level Modelling for any Logic Circuit in TeluguПодробнее

How to write a Verilog code in Data Flow & Gate Level Modelling for any given Logic Circuit | VIVADOПодробнее

Verilog code for BCD to Excess 3 || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

verilog for combinational circuits-2: full adder in 3 modelling stylesПодробнее

Verilog code for combinational circuits-1: Half adder in 3modelling stylesПодробнее

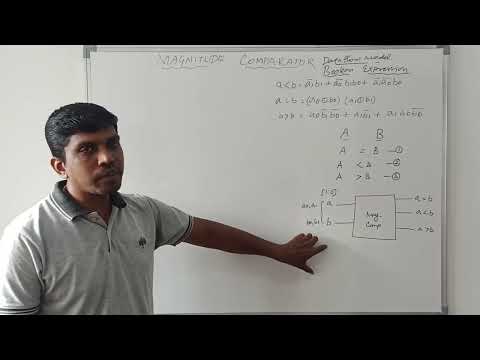

Magnitude Comparator Verilog HDL using Data Flow Model || S Vijay Murugan || Learn ThoughtПодробнее

Basics of VERILOG | DataFlow Level Modeling - Half & Full Adder & Subtractor, Mux, Decoder | Class-9Подробнее