Structural Verilog Code for 2-to-4 Decoder

Understanding 2:4 decoder using verilogПодробнее

verilog rtl code for 2*4 decoder #case_statementПодробнее

2×4 decoder using verilogПодробнее

8 to 1 Mux Using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

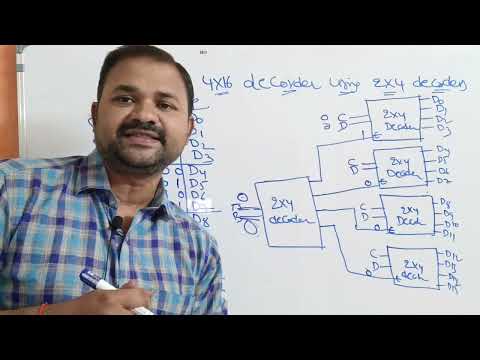

Construction of 4 * 16 Decoder using 2 * 4 Decoders | Digital Logic Design |Digital ElectronicsПодробнее

Construction of 3 * 8 Decoder using Two 2 * 4 Decoders | Digital Logic Design |Digital ElectronicsПодробнее

#31 2:4 Decoder | Verilog Design and Testbench Code | VLSI in TamilПодробнее

How to Write 2 to 4 Decoder Verilog HDL Program? // Behavioral Model // S Vijay MuruganПодробнее

2:4 decoder |video 1| Verilog code | HDL experiment |18ecl58Подробнее

Design of 4 bit Comparator || Verilog HDL Program || Learn Thought || S VIJAY MURUGANПодробнее

Decoder 2: 4 | verilog code for 2 to 4 decoder in data flow and behavioral descriptionПодробнее

3 to 8 decoder using two 2 to 4 decoder in Quartus PrimeПодробнее

2 to 4 Decoder in Quartus PrimeПодробнее

verilog code for 2:1 Mux in all modeling stylesПодробнее

Design of 8 to 3 Encoder Using Verilog HDL | VLSI Design | S VIjay MuruganПодробнее

Design a Verilog Code for 2 to 4 Decoder | VLSI Design | S VIJAY MURUGANПодробнее

4-Bit Ripple Carry Adder Verilog HDL Program | Gate Level Modeling | VLSI Design | S VIJAY MURUGANПодробнее

Verilog HDL PROGRAM | Full Adder | Gate Level Modeling | VLSI Design | S VIJAY MURUGANПодробнее

4 to 1 MUX Verilog Code using Gate Level Modelling | VLSI Design | S VIJAY MURUGANПодробнее