sequential logic implementation using registers

Register Implementation with Timing Diagram | Explained in Just 15 minutes.Подробнее

RISC-V Processor Design Course - Lec 3 - Multiplexers & Sequential LogicПодробнее

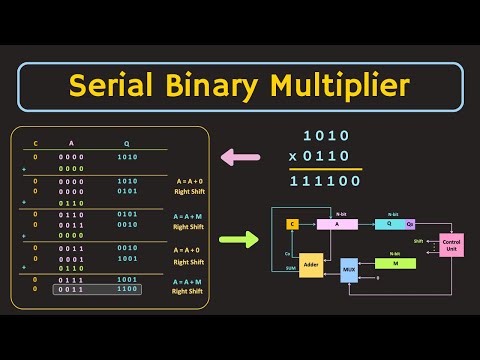

Serial Binary Multiplier / Sequential Binary Multiplier (using Add and Shift Method)Подробнее

Mastering Sequential Circuits: Flip-Flops, Registers, and Counters in LogisimПодробнее

WHAT Are Counters And Registers In Digital Logic Design! Register predetermined sequence of binaryПодробнее

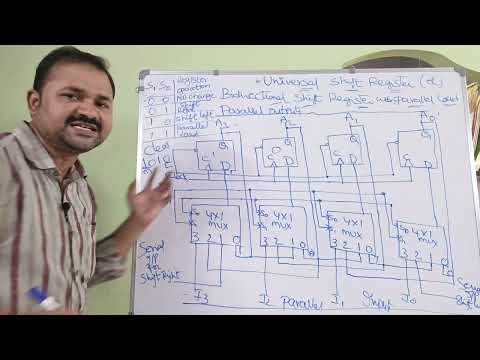

Universal Shift Register || Bidirectional Shift Register with Parallel Load || Digital Logic DesignПодробнее

SIPO Shift Register || Serial In Parallel Out Shift RegisterПодробнее

Shift Registers || Types of Shift Registers || SISO || SIPO || PISO || PIPO || Digital ElectronicsПодробнее

Problem 6.7: Draw the logic diagram of a four‐bit register with four D flip‐flops and four 4 × 1 muxПодробнее

Problem 6.6: Design a four‐bit shift register with parallel load using D flip‐flops with control IPПодробнее

Clocked CMOS Dynamic Register - VLSIПодробнее

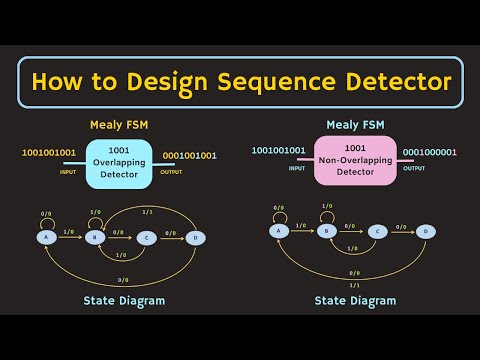

Sequence Detector | How to Design a Finite State Machine ? Step By Step Guide with ExamplesПодробнее

Linear Feedback Shift Register (LFSR) in verilogПодробнее

Bidirectional Shift Register - Implementation in LogisimПодробнее

Applications of Shift Register | Ring Counter and Johnson Counter, PRBS GeneratorПодробнее

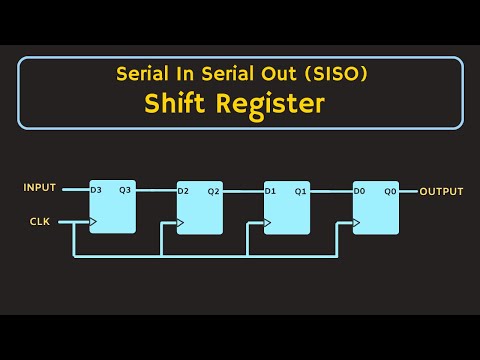

Shift Register : Serial In Serial Out (SISO) Register Explained | Bidirectional Shift RegisterПодробнее

Introduction to Registers | What is Shift Register? Types of Shift RegistersПодробнее

Counter Implementation/ Counter design Using JK flip flop.Подробнее

Intro to Linear Feedback Shift Registers and Sequence GeneratorsПодробнее

Lec - 48: Shift Registers | SISO, SIPO, PISO, PIPOПодробнее