Logic Gates Explained 1/2

2 :1 MUX VERILOG CODE EXPLANATIONПодробнее

L- 1, Unit - 2 || logic gate, Application & it's Types || Digital Electronics || #computer #digitalПодробнее

Example 2 | K-Map | 4-Variable Boolean Function | Σ(0,1,2,3,6,12,13,14,15) Explained in TeluguПодробнее

📘DTE Ch 2 – Part 1 – Logic Gates & Boolean Laws Simplified | #dte #msbtechnical #diplomaengineeringПодробнее

#19 2:1 Multiplexer (MUX) in Verilog 🔀 Explained with Code | #Verilog #MUX #Electronics #ShortsПодробнее

Design 4:1 Multiplexer Step by Step Explanation | MUX truth table, Circuit Diagram #computerscienceПодробнее

2 a Model Paper Solution Explained Module 1 6th Sem VLSI Design & Testing ECE 2022 Scheme VTUПодробнее

Binary Subtraction Explained: 1's and 2's Complement MethodsПодробнее

Half Adder Using 2×1 and 4×1 Multiplexers | Multiplexer as universal logicПодробнее

K Map SOP in Tamil | K Map POS in Tamil | Basic Electrical and Electronics Engineering in TamilПодробнее

Multiplexer as Universal Logic | All Logic Gates Using 2-to-1 MUX ExplainedПодробнее

1:2 Demultiplexer Logic Circuit | Fully Explain | Digital ElectronicsПодробнее

1 NMOS Enhancement Transistor Concept Explained Module 2 6th Sem VLSI ECE 2022 Scheme VTUПодробнее

1-Bit and 2-Bit Magnitude Comparator | Digital Electronics Explained | VRacademyПодробнее

"7 Logic Gates Using Arduino Mega | 2 Buttons + 1 LED | C++ Beginner Project"Подробнее

1:2 Demultiplexer: Logic Gates Step-by-Step | Designing a 1:2 Demux | Build a 1:2 DemultiplexerПодробнее

short trick for 1 's and 2's complement#cse#digitalelectronics#computerscience#ece#gate#numbersystemПодробнее

CMOS transmission gates | DC analysis | Part-1/2 | Digital Systems Design | Lec-118Подробнее

Understanding Multiplexers | 2:1 and 4:1 MUX Explained in Digital Design|| All about VLSI||Подробнее

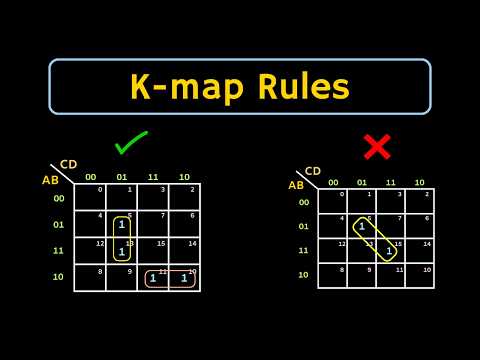

Karnaugh Map (K-map) Rules for Simplification ExplainedПодробнее