How to use Signed and Unsigned in VHDL

#07 ~ How to Write Flexible VHDL Code for FPGA | VHDL Attributes & Data Types | Course 04 #vhdlПодробнее

VHDL data types I STD_LOGIC | Signed & Unsigned | Digital Systems Design | Lec-19Подробнее

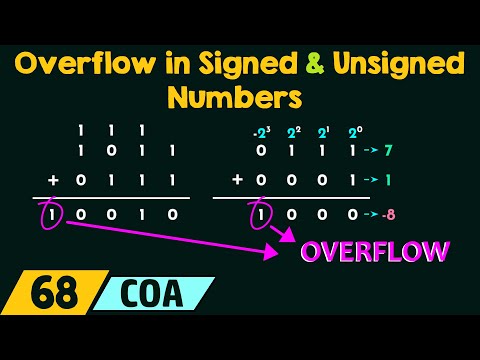

Overflow in Signed and Unsigned NumbersПодробнее

Quiz 36 - VHDL : Data Objects and Types | #shortsПодробнее

Electronics: VHDL: I can port map std_logic_vector to a signed or unsigned port, why?Подробнее

Electronics: Range-limited integers or unsigned/signed in VHDLПодробнее

Electronics: VHDL - Cheapest-Fastest unsigned to signed binary number converter (2 Solutions!!)Подробнее

Lecture 13 Signed and Unsigned Data Types, Data ConversionПодробнее

Flash VHDL : les conversions entre INTEGER, STD_LOGIC_VECTOR, SIGNED et UNSIGNEDПодробнее

FPGA Math - Add, Subtract, Multiply, Divide - Signed vs. UnsignedПодробнее

005 18 Signed Unsigned in vhdl verilog fpgaПодробнее