How to Generate Multicycle Path Constraints in HDL Coder

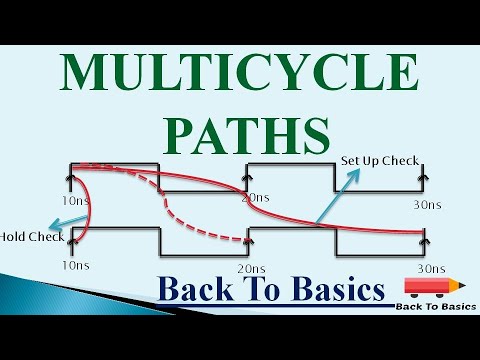

Multicycle Paths | STA | Back To BasicsПодробнее

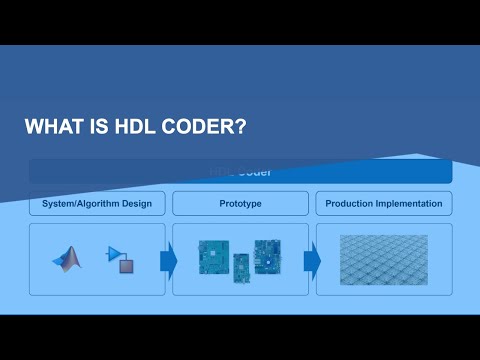

HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink VideoПодробнее

Multicycle PathsПодробнее

Live Webinar: Unlocking the Power of HDL Coder - Accelerating Hardware DevelopmentПодробнее

Designing and Optimizing MATLAB Algorithms for HDL Code GenerationПодробнее

The Multi cycle Path in VLSIПодробнее

PD Topic #34: Multi-Cycle Paths - Fast to Slow Synchronous Clocks | Setup & Hold MCPПодробнее

What Is HDL Coder?Подробнее

Best Practices for Using Stateflow for HDL Code GenerationПодробнее

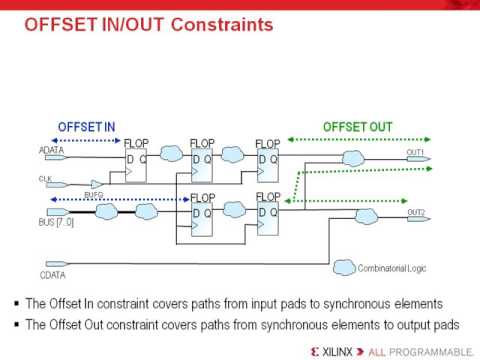

Xilinx® Training Global Timing ConstraintsПодробнее

Design of Multi Cycle Data PathПодробнее

Timing Constraints: How do I connect my top level source signals to pins on my FPGA?Подробнее

Multi Sign Assembly OptionПодробнее

Generate HDL for a Deep Learning ProcessorПодробнее

HDL Coder Clock Rate Pipelining, Part 1: Introduction - MATLAB and Simulink videoПодробнее