How to convert a 2:1 MUX into a NOT gate?

#AOI #and-orgate implementationof#2*1 mux #lec10Подробнее

Design 2 to 1 Mux Using CMOS Switch || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Switch Level Verilog Code for NOR Gate || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Switch Level Verilog Code for NAND Gate in Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

8 to 1 Mux Using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

4 to 1 Mux using 2 to 1 Mux || Test Bench Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

NAND Gate using 2 to 1 Mux || Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

Implementation of 2:1 Mux to basic gates #digitalelectronics#vlsi #verilog#digitalindia#influencerПодробнее

How to design 2:1 multiplexer using logic gates in breadboard I 2:1 multiplexer Practical IПодробнее

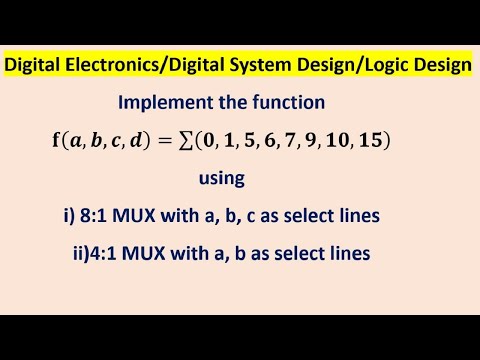

Implement the function 𝐟(𝒂,𝒃,𝒄,𝒅)=∑(𝟎,𝟏,𝟓,𝟔,𝟕,𝟗,𝟏𝟎,𝟏𝟓) using8:1 MUXПодробнее

2:1 Multiplexer Using Primitives, Always and Continuous AssignmentsПодробнее

Implementation of 2×1 MUX using NAND & NOR GatesПодробнее

Design gates (NOT/ OR/ AND/ XOR/ XNOR/ Full adder) using muxПодробнее

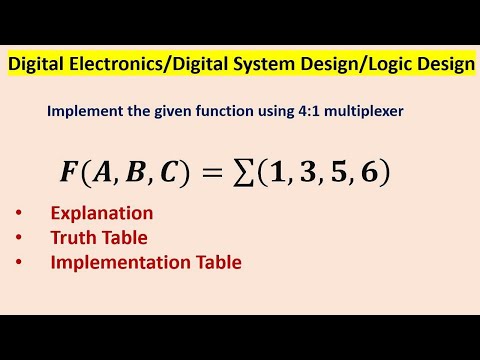

Implement the given function using 4:1 multiplexer. 𝑭(𝑨,𝑩,𝑪)=∑(𝟏,𝟑,𝟓,𝟔)Подробнее

116 Quadruple 2 to 1 Multiplexer Logic Circuit and ExplanationПодробнее

Implementation of NAND Gate using 2:1 Mux in verilogПодробнее

Implementing Not Gate using 2:1 Mux in VerilogПодробнее

Implementation of logic gates using 2x1 Multiplexer @ExploretheWAYПодробнее

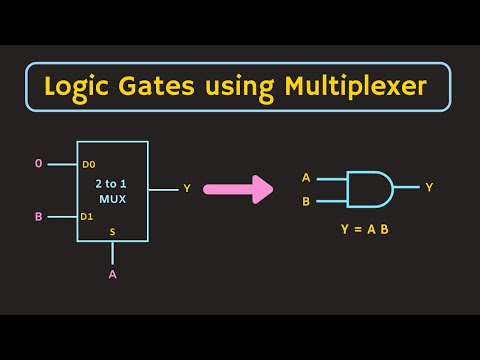

Logic Gates using Multiplexer | How to implement a logic gate using the multiplexer ?Подробнее