FPGA Bit Counter Demonstration

4-bit asynchronous counter with 7 segment display #arduino #arduinoprojectПодробнее

32-bit Counter Design in Vivado | Verilog Tutorial for Xilinx FPGAПодробнее

FPGA: Binary-Coded-Decimal (base 10) counter DEMOПодробнее

Lession 16: 3bit Counter with 7-Segment Display on FPGAПодробнее

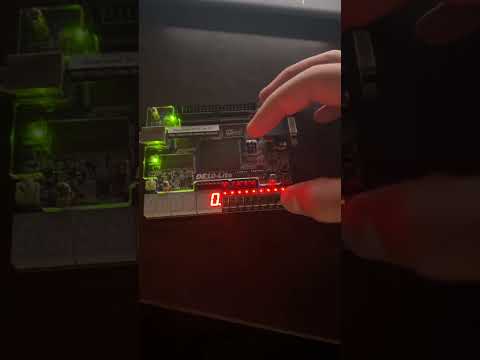

FPGA Design on Terasic DE1-SoC | 10-bit MSB Counter with LEDs Using Intel Quartus Prime LiteПодробнее

FPGA Design on Terasic DE1-SoC | 32-bit Counter with LEDs Using Intel Quartus Prime LiteПодробнее

Counter implementation on FPGA |Boolean Board |Подробнее

Learning FPGA Together Part 12: Counters 1/2Подробнее

Count Down FPGA BoardПодробнее

Shorter Demonstration of 3-Bit Binary Up/Down Counter With ResetПодробнее

2 bit up counter using flip flop 🔼0️⃣1️⃣2️⃣3️⃣ #digitalelectronics #electronic #proteus8Подробнее

counter using FPGA 😉🔥Подробнее

Lab 1 Demo (0-9 4-bit Binary to BCD)Подробнее

VHDL counter 0 to 9999 with FSM inside Cyclone IV FPGA 🤖🕟 #vhdl #fpga #cycloneПодробнее

Lecture 5: Implementing 4-bit Counter on 7 Segment Display of FPGA (DE1 Altera Cyclone V SoC)Подробнее

Lecture 4: Implementing 4-bit Counter on FPGA (DE1 Altera Cyclone V SoC)Подробнее

Counters Theory & Verilog code writing with Testbench | Detailed Explanation | VLSI Interview GuideПодробнее

FPGA Design Tutorial (Verilog, Simulation, Implementation) - Phil's Lab #109Подробнее

VHDL code of 6 bit Up counter | FPGA #shortsvideo #youtubeshorts #maker #fpga pga #vhdl #shortsПодробнее

COUNTER WITH 7 SEGMENT DISPLAY # VHDL #fpga #shorts #challengeПодробнее