FIFO in Verilog on Basys3 FPGA

UART in Verilog on Basys3 FPGA using PuTTYПодробнее

FIFO Buffer Memory in Verilog | FPGAПодробнее

FPGA - FIFO in Verilog #09Подробнее

Designing a First In First Out (FIFO) in VerilogПодробнее

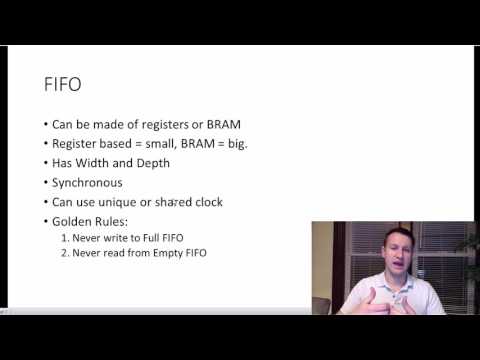

What is a FIFO in an FPGAПодробнее

Learn Verilog By Examples - Single Clock FIFOПодробнее

FPGA InsideOut Session2 | FIFO design, modelling and verificationПодробнее

ASYNCHRONOUS FIFO SIMULATION DEMOПодробнее

Candy Machine State Machine in Verilog on Basys3 FPGA using VivadoПодробнее

Synchronous fifo design in verilogПодробнее

Verilog on Intel (Altera) FPGA Lesson 12: FIFO 04 – Synchronous FIFO 03: TestBenchПодробнее

FIFO SYNTHESIS VIDEO DEMOПодробнее

FPGA Programming with Verilog : Full Adder BASYS3Подробнее

Verilog on Intel (Altera) FPGA Lesson 9: FIFO 01 – IntroductionПодробнее

FIFO Clock Domain Crossing (CDC) | FIFO Basics | Asynchronous FIFO | Synchronous FIFO | FIFO DesignПодробнее

Verilog on Intel (Altera) FPGA Lesson 11: FIFO 03 – Synchronous FIFO 02Подробнее

Modelling of Memory Part-3| Modelling Synchronous FIFO|Verilog|Part 26Подробнее