Execute Instructions on CPU Datapath

Multicycle Data path diagram II Exception II Computer ArchitectureПодробнее

CPU Design Basics: Simple Processor Architecture & Instruction Execution Explained!Подробнее

The following table includes the five individual stages of the datapath. Compute the following in d…Подробнее

Pipelining in Computer Architecture Example | Ai*Bi+Ci #architectureПодробнее

Datapath for R-type InstructionПодробнее

CO29c - Single Bus Processor | Branch InstructionsПодробнее

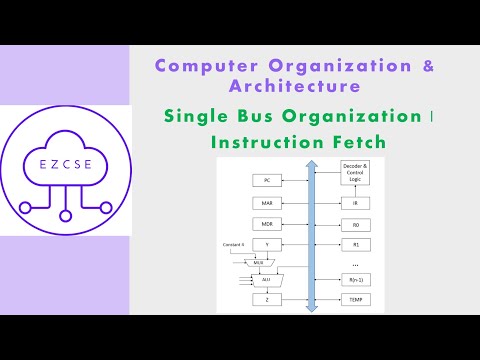

CO29 - Single Bus Organization Processor | Instruction FetchПодробнее

Lec 6: Introduction to RISC Instruction PipelineПодробнее

Computer Architecture and Organization The Processor Datapath, Pipelining and Hazards in TamilПодробнее

MIPS Single Cycle Explained: LW, ADD, BEQПодробнее

Lecture 9: Designing RISC-V Microarchitecture IVПодробнее

L - 30 | Unit - 3 | Execution of complete instruction | Computer Organization and ArchitectureПодробнее

[CS61C FA20] Lecture 19.4 - Single-Cycle CPU Datapath II: Adding JALR to DatapathПодробнее

![[CS61C FA20] Lecture 19.4 - Single-Cycle CPU Datapath II: Adding JALR to Datapath](https://img.youtube.com/vi/l5ML8v9R8w8/0.jpg)

[CS61C FA20] Lecture 19.7 - Single-Cycle CPU Datapath II: SummaryПодробнее

![[CS61C FA20] Lecture 19.7 - Single-Cycle CPU Datapath II: Summary](https://img.youtube.com/vi/1WTP44UAtp4/0.jpg)

[CS61C FA20] Lecture 18.2 - Single-Cycle CPU Datapath I: Building a RISC-V ProcessorПодробнее

![[CS61C FA20] Lecture 18.2 - Single-Cycle CPU Datapath I: Building a RISC-V Processor](https://img.youtube.com/vi/8Dv725H2-Os/0.jpg)

[CS61C FA20] Lecture 19.6 - Single-Cycle CPU Datapath II: Adding U-TypesПодробнее

![[CS61C FA20] Lecture 19.6 - Single-Cycle CPU Datapath II: Adding U-Types](https://img.youtube.com/vi/8q8l0tXs_Lc/0.jpg)

[CS61C FA20] Lecture 20.2 - Single-Cycle CPU Control: Datapath ControlПодробнее

![[CS61C FA20] Lecture 20.2 - Single-Cycle CPU Control: Datapath Control](https://img.youtube.com/vi/wM85LGWD54U/0.jpg)

[CS61C FA20] Lecture 19.1 - Single-Cycle CPU Datapath II: Supporting LoadsПодробнее

![[CS61C FA20] Lecture 19.1 - Single-Cycle CPU Datapath II: Supporting Loads](https://img.youtube.com/vi/TnDpXz75SGA/0.jpg)

[CS61C FA20] Lecture 18.3 - Single-Cycle CPU Datapath I: R-Type Add DatapathПодробнее

![[CS61C FA20] Lecture 18.3 - Single-Cycle CPU Datapath I: R-Type Add Datapath](https://img.youtube.com/vi/f1cZGi4mZqo/0.jpg)

[CS61C FA20] Lecture 19.3 - Single-Cycle CPU Datapath II: Implementing BranchesПодробнее

![[CS61C FA20] Lecture 19.3 - Single-Cycle CPU Datapath II: Implementing Branches](https://img.youtube.com/vi/XTgyEsFRvWg/0.jpg)