Design and implementation of reconfigurable ALU on FPGA

ALU FPGA ExampleПодробнее

Design and implementation of floating point ALU in FPGAПодробнее

Exp-4-ALU 32bit version using Xilinx FPGA FlowПодробнее

Design and Analysis of FPGA Based 32 Bit ALU Using Reversible GatesПодробнее

VHDL code for 4 bit ALU and Realization on FPGA development BoardПодробнее

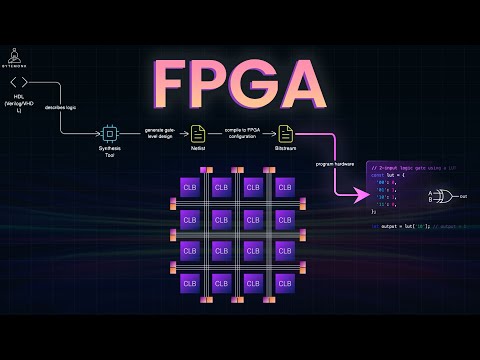

FPGA in HFT Systems Explained | Why Reconfigurable Hardware Beats CPUsПодробнее

Floating Point FPGA ArchitectueПодробнее

Exp-4- 4 bit ALU implementation using Xilinx FPGAПодробнее

VHDL code for 4 bit ALU and Realization on FPGA development BoardПодробнее

8 bit ALU for Practical Design with Xilinx FPGAПодробнее

Design and Implementation of Arithmetic Logic Unit in HDLПодробнее

Implementation of a VR4300 ALU ShifterПодробнее

ALU implementation on Xilinx FPGA Part 2Подробнее

How to Implement 8-Bit ALU with Structural Modeling in VHDL on BASYS3Подробнее

Part 3: Step-by-Step Guide: Simulating a 4-Bit ALU in Verilog Using Xilinx VivadoПодробнее

Design and Implementation of 4-Bit ALU for Low-Power using Adiabatic Logic based on FINFETПодробнее

Clock Gating Based Energy Efficient ALU Design and Implementation on FPGAПодробнее

FPGA Basic ALU DemoПодробнее

A Reconfigurable Low Power FPGA Design with Autonomous Power Gating and LEDR Encoding|IEEE VLSI puneПодробнее