CMOS logic gate - 4-input function

Logical effort of inverter, NAND and NOR gateПодробнее

L14-C Construction of Pull up (PUN) and Pull down Network (PDN) in CMOSПодробнее

Domino Logic | np CMOS | Cascading dynamic gates | VLSI | Lec-96Подробнее

Pass transistor logic | Static CMOS circuit design | VLSI | Lec-93Подробнее

Complementary CMOS circuits | Propagation delay | VLSI | Lec-91Подробнее

Implementation of Boolean Expression using CMOS || VLSI Design || S Vijay Murugan || Learn ThoughtПодробнее

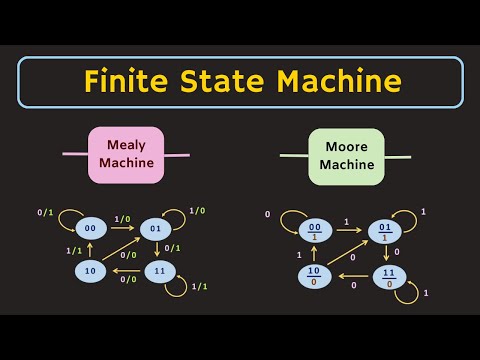

Finite State Machine Explained | Mealy Machine and Moore Machine | What is State Diagram ?Подробнее

Dynamic CMOS logic - 1 | Forms of CMOS Logic | VLSI | Lec-56Подробнее

Gate logic | nMOS, CMOS and BiCMOS | VLSI | Lec-54Подробнее

CMOS | 2-input NAND and NOR gates | Layout diagram | VLSI | Lec-34Подробнее

CMOS logic functions | Stick diagram | VLSI | Lec-30Подробнее

Pass Transistor Logic Explained | How to Implement Logic Gates using Pass Transistor Logic ?Подробнее

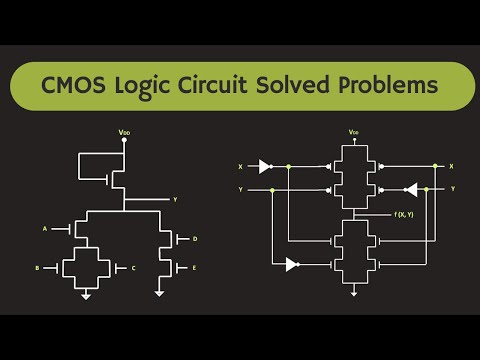

Solved Problems on CMOS Logic Circuits | Digital ElectronicsПодробнее

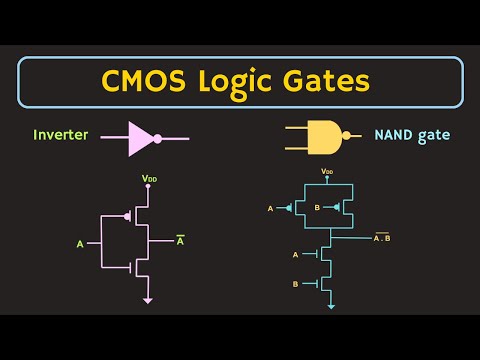

CMOS Logic Gates Explained | Logic Gate Implementation using CMOS logicПодробнее

Understanding CMOS Logic Gates: Transistor-Level Schematics Explained!Подробнее

Transistor Logic Gates - NAND, AND, OR, NORПодробнее

VLSI Design | Sequential CMOS Logic Circuits Part-2 | AKTU Digital EducationПодробнее

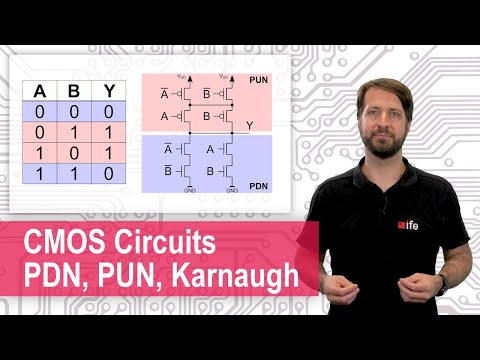

CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XORПодробнее

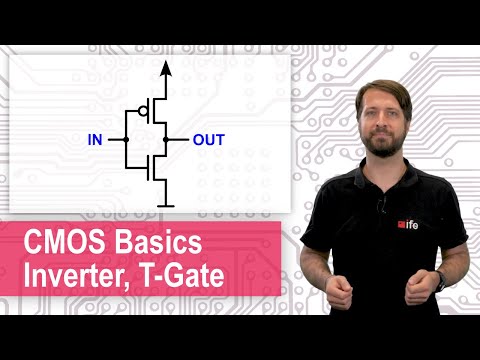

CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch UpПодробнее

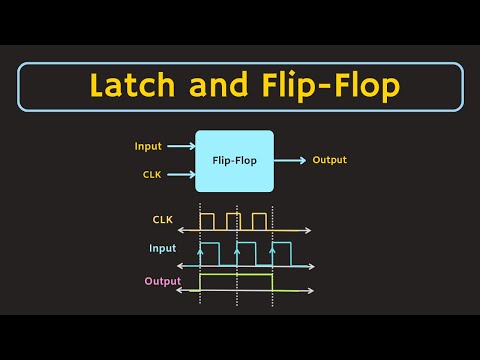

Latch and Flip-Flop Explained | Difference between the Latch and Flip-FlopПодробнее