Building a CPU on an FPGA, part 1

Let's build the singularity part 1Подробнее

The Mister FPGA Computer Game System [Part 1]Подробнее

![The Mister FPGA Computer Game System [Part 1]](https://img.youtube.com/vi/VwXX3J1onkk/0.jpg)

FPGA CPU - Part 1 - Switches, LEDs, & 7-Segment DisplaysПодробнее

FPGA Design: Architecture and Implementation - Speed (Timing) Optimization - Part 1Подробнее

Run RISC V Processor on FPGA Part 1 Get the VerilogПодробнее

FPGA Concepts Part 1: Ye Olden DaysПодробнее

FPGA Polarfire Icicle Libero Part 1 - Build the Reference DesignПодробнее

Software Emulators vs FPGAsПодробнее

Zynq Part 1: Vivado block diagram (no Verilog/VHDL necessary!)Подробнее

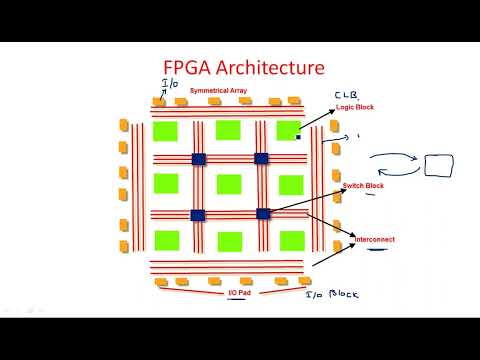

FPGA Architecture | Configurable Logic Block ( CLB ) | Part-1/2 | VLSI | Lec-75Подробнее

FPGA #1 - An Overview of Programmable Logic DevicesПодробнее

Build A Soft Core CPU - Part Three - NIOS II in Intel FPGAПодробнее

FPGA Parallelism vs Processor Architecture 1/2 (Marco D. Santambrogio)Подробнее

Digital Design & Computer Architecture - Labs: Introduction to the Labs and FPGAs (Spring 2023)Подробнее

FPGA/SoC Board Bring-Up Tutorial (Zynq Part 1) - Phil's Lab #96Подробнее

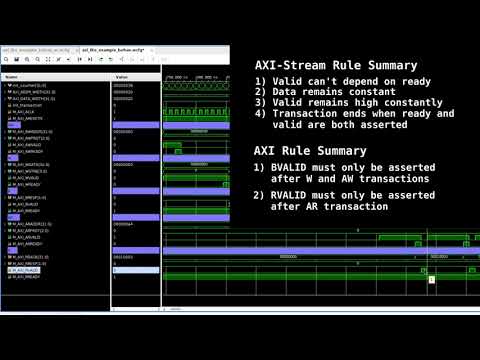

AXI Introduction Part 1: How AXI works and AXI-Lite transaction exampleПодробнее

486SocketBlaster: A DIY voltage adapter for the 486 CPU (part 1)Подробнее

Build A Soft Core CPU - Part Two - RISC-V in Xilinx FPGAПодробнее

Simple beginnings LETA eliminator Part 1Подробнее

Architecture All Access: Neuromorphic Computing Part 1Подробнее