Asynchronous FIFO | Clock Domain Crossing (CDC) | FIFO RTL Design

CDC Solutions Designs [7]: fifoПодробнее

![CDC Solutions Designs [7]: fifo](https://img.youtube.com/vi/bZPzLTJ3ieE/0.jpg)

Clock Domain Crossing (CDC), Synchronizers and FIFOsПодробнее

Mastering Clock Domain Crossing (CDC)Подробнее

SystemVerilog - Asynchronous FIFO RTL Design Part 2: async reset, sync releaseПодробнее

SystemVerilog - Asynchronous FIFO RTL Design Part 1: GirişПодробнее

FIFO Depth Calculation | How to Calculate FIFO Depth | Clock Domain crossing | CDC | VLSI InterviewПодробнее

FIFO Depth Calculation | How to Calculate FIFO Depth | Clock Domain crossing | CDC | VLSI InterviewПодробнее

Asynchronous FIFO Design | Async FIFO | Basics of Asynchronous FIFO | Asynchronous FIFO VerilogПодробнее

Top VLSI Interview Questions | VLSI Interview Questions and Answers | Interview Question and AnswerПодробнее

Synchronous FIFO Design | Basics of Synchronous FIFO | FIFO Full | FIFO Empty ExplainedПодробнее

FIFO Clock Domain Crossing (CDC) | FIFO Basics | Asynchronous FIFO | Synchronous FIFO | FIFO DesignПодробнее

VLSI - CDC - Async FIFO DesignПодробнее

CDC Synchronizer | 2 flop synchronizer | Two flop synchronizer |2 stage synchronizer| VLSI InterviewПодробнее

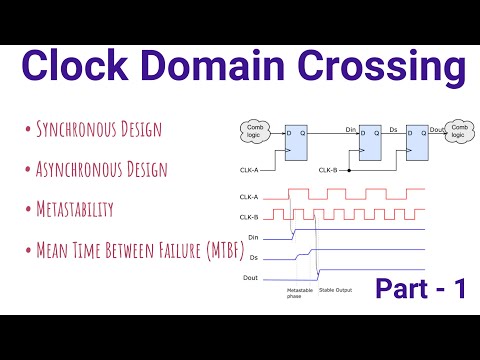

Clock Domain Crossing (CDC) Basics | Techniques | Metastability | MTBF | VLSI Interview questionsПодробнее

Electronics: Asynchronous FIFO in clock domain crossingПодробнее

Session 5: Clock Domain CrossingПодробнее