AND gate using CMOS | VLSI Design | S Vijay Murugan | Learn Thought

CMOS Implementation and Stick Diagram || Learn Thought || S Vijay MuruganПодробнее

XOR Gate Using Pass Transistor || Learn Thought || S Vijay MuruganПодробнее

Tristate Buffer Verilog HDL Code || Learn Thought || S Vijay MuruganПодробнее

BCD to Excess 3 Test Bench Verilog Code || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Verilog code for BCD to Excess 3 || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Implementation of Half Adder Using CMOS || VLSI Design || Learn Thought || S Vijay MuruganПодробнее

Implementation of 2 to 1 Mux using CMOS || VLSI Design || Learn Thought || S Vijay MuruganПодробнее

Design 2 to 1 Mux Using CMOS Switch || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Switch Level Verilog Code for NOR Gate || Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Switch Level Verilog Code for NAND Gate in Verilog HDL || Learn Thought || S Vijay MuruganПодробнее

Switch Level CMOS Inverter || Verilog HDL || S Vijay Murugan || Learn ThoughtПодробнее

CMOS Switch in Verilog HDL|| Switch Level Modeling || S Vijay Murugan || Learn ThoughtПодробнее

Implementation of EX OR and EX NOR Gate Using 2 to 1 Multiplexer || Learn Thought || S Vijay MuruganПодробнее

Difference between FPGA & ASIC in VLSI Design || S VIJAY MURUGAN || Learn ThoughtПодробнее

4 Bit Ring Counter Using Verilog HDL Code || S Vijay Murugan || Learn ThoughtПодробнее

ASIC Design Flow in VLSI Design || Learn Thought || S Vijay MuruganПодробнее

Comparison of Design Style in VLSI Design || S Vijay Murugan || Learn ThoughtПодробнее

PART 1 - Design 2 Bit Comparator Using Pass Transistor Logic |A=B || S Vijay Murugan | Learn ThoughtПодробнее

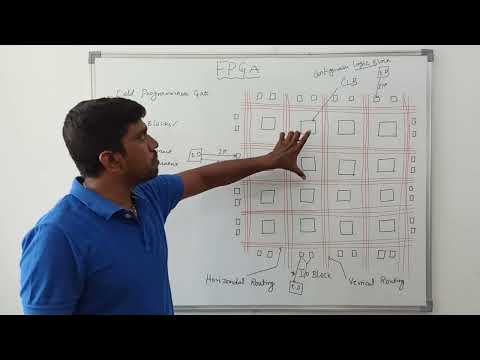

Field Programmable Gate Array in VLSI Design || Learn Thought || S Vijay MuruganПодробнее

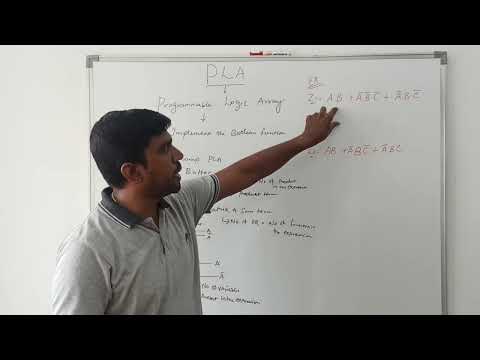

Programmable Logic Array (PLA) in VLSI Design || S Vijay Murugan || Learn ThoughtПодробнее