#3: Verilog Simulation in Modelsim

Design of 3 bit Synchronous up counter- Verilog program using Modelsim softwareПодробнее

7 Testbench file for 3 Inputs Neuron Model, and ModelSim SimulationПодробнее

Xilinx ISE: Design and simulate VERILOG HDL CodeПодробнее

Modelsim tutorial 3: Verilog code for an buffer circuit and its test bench for verificationПодробнее

ModelSim & Verilog - Язык Проектирования Схем §11 Часть 3/5Подробнее

Lab-1 Creating and simulating a project in Modelsim Verilog code for NOT gate | Dr. Muntazir HussainПодробнее

Modelsim/QuestaSim Simulator Walk Through (Tutorial For Beginners) Part-1Подробнее

How to write Verilog HDL module for Priority Encoder using ModelSimПодробнее

How to write Verilog HDL module for 3 to 8 Decoder using ModelSimПодробнее

How to write Verilog HDL module for ALU using ModelSimПодробнее

How to program And Gate in Verilog HDL programming using ModelSimПодробнее

Modelling of Memory Part-3| Modelling Synchronous FIFO|Verilog|Part 26Подробнее

ALU Design in Verilog with Testbench | Simulation in Modelsim | Arithmetic Logic UnitПодробнее

Verilog Code for 2 to 4 Decoder in Modelsim with TestBench | Verilog TutorialПодробнее

Implementation of 4:1 Multiplexer Circuit using Verilog HDLПодробнее

Verilog Simulation of 4-bit Multiplier in ModelSim | Verilog TutorialПодробнее

4-Bit Full Adder Verilog Code and Testbench in ModelSim | Verilog TutorialПодробнее

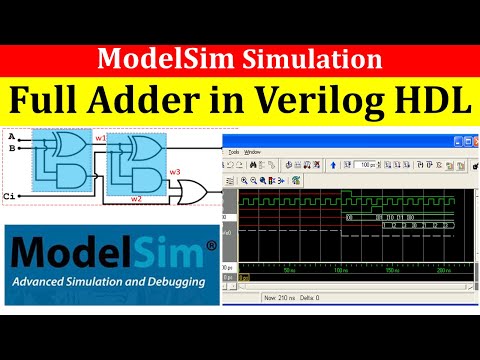

Full Adder Design using Gate Level Modeling in ModelSim | Verilog TutorialsПодробнее

Verilog Coding of Gate Level Design | Gate Level Design in ModelSim | Verilog TutorialПодробнее