002 15 Types of Data Object in vhdl verilog fpga

002 02 Entity Architecture Pair in vhdl verilog fpgaПодробнее

Data objects in VHDLПодробнее

Predefined DataTypes in vhdl verilog fpgaПодробнее

002 07 Event and Transaction in vhdl verilog fpgaПодробнее

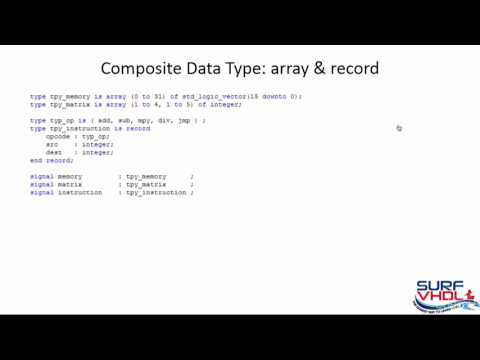

004 17 VHDL User defined data type in vhdl verilog fpgaПодробнее

001 14 Predefined DataTypes in vhdl verilog fpgaПодробнее

007 20 Subtype in vhdl verilog fpgaПодробнее

004 09 VHDL Delay Modeling in vhdl verilog fpgaПодробнее

007 12 Generics in vhdl verilog fpgaПодробнее

001 05 Structural Modeling in vhdl verilog fpgaПодробнее

008 13 Driver and Source in vhdl verilog fpgaПодробнее

Data Object Classes | VHDL | Tutorial 1Подробнее

002 02 Introduction to Modelsim in vhdl verilog fpgaПодробнее

002 Bonus2 Test bench Write to File in vhdl verilog fpgaПодробнее

Data types in VHDLПодробнее

003 16 bit vs ulogic vs std logic in vhdl verilog fpgaПодробнее

004 04 Coding Style in vhdl verilog fpgaПодробнее

001 21 Sequential Modeling in vhdl verilog fpgaПодробнее

003 08 Behavioral Model Example in vhdl verilog fpgaПодробнее